IMEC专家详解3nm晶体管结构,四大关键工艺步骤揭秘。芯东西8月13日消息,随着三星、英特尔、台积电、IBM等半导体厂商相继发布新晶体管结构的进展,半导体行业正处于晶体管结构转变的前夜。虽然芯片行业从不急于采用新的晶体管结构进行量产,但如果想要生产3nm或2nm制程的逻辑芯片,英特尔、三星、台积电等厂商必须从当前的鳍式场效应晶体管结构(FinFET)逐渐过渡到纳米片结构(Nanosheets)。堀口直人是IMEC(比利时微电子研究中心)逻辑CMOS微缩项目主管,曾在富士通实验室和加州大学圣巴巴拉分校等机构任职。目前,堀口直人的研发重点就是2nm以下的CMOS器件。以下是芯东西对堀口直人就3nm晶体管结构发展回顾的完整编译。

▲IMEC逻辑CMOS微缩项目主管堀口直人

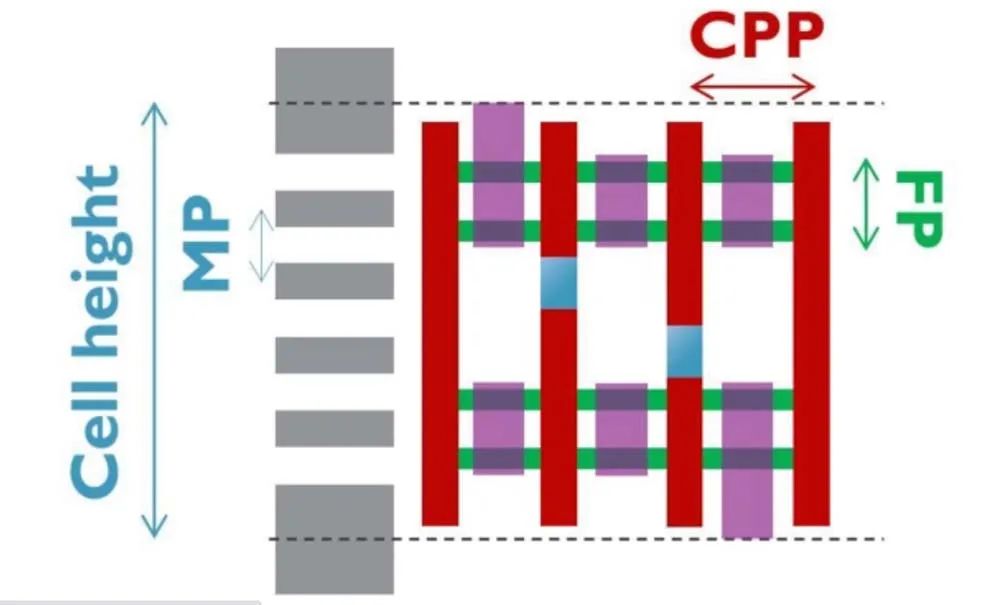

一直以来,为了追寻摩尔定律,半导体产业在微缩逻辑CMOS尺寸上做出了相当大的努力。一种主要的方法是通过减少金属连线(或轨道)来降低单元高度(cell height),单元高度也就是每个单元的金属线数量乘以金属间距(metal pitch,即金属连线的最小宽度+金属连线之间的最小间距)。对于FinFET结构来说,通过将一个标准单元内的鳍片(Fin)的数量从3个减少到2个,就可以在性能上跃进一大步。

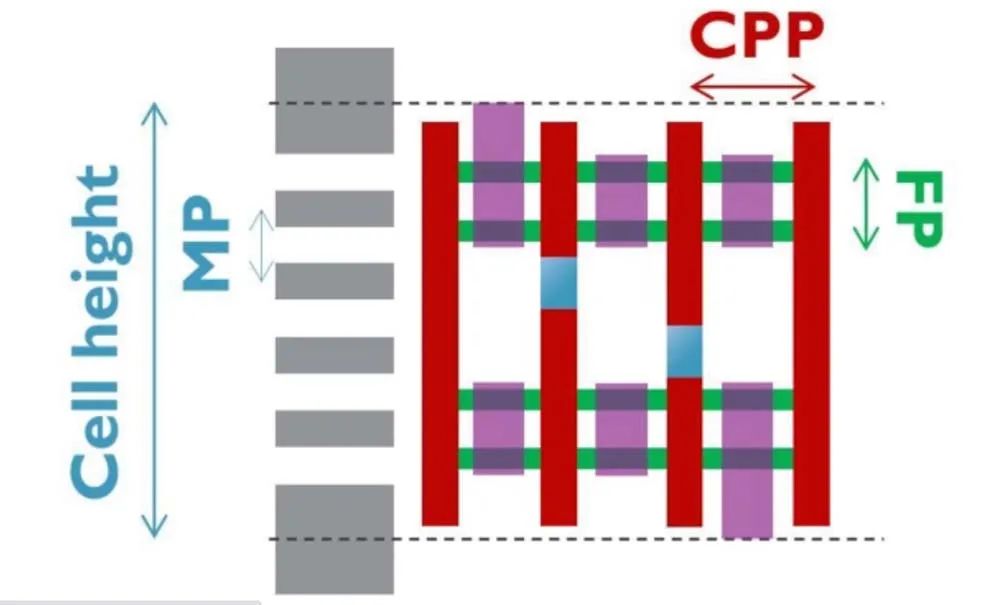

▲标准逻辑单元示意图(CPP=接触多晶间距,FP=鳍片间距,MP=金属间距;单元高度=每个单元的金属线数x金属间距)

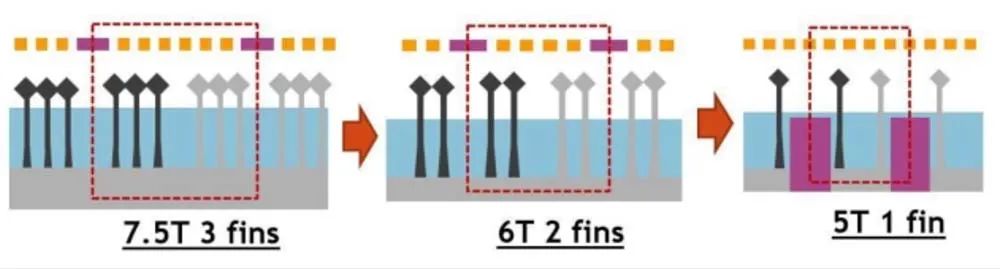

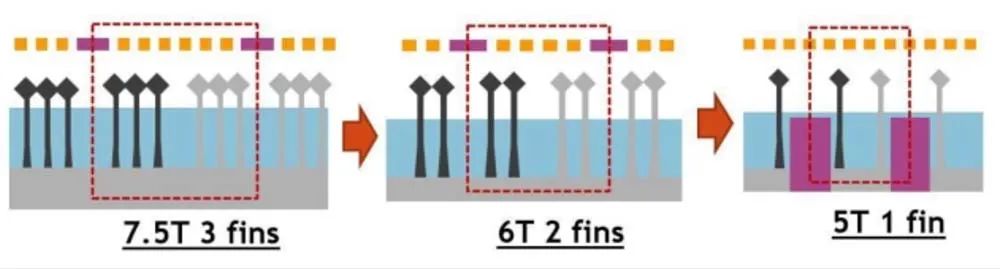

标准单元内单元高度中有几条金属连线则是一个重要指标,通常在单元高度范围内有几条金属线就称为几T。随着鳍片减少,单元高度逐渐变小,标准单元从7.5T变为了6T。然而这种缩小牺牲了内部的驱动电流和可变性,为了弥补这些性能的退化,鳍片在单元的高度微缩中也变得越来越高。但是到了5T FinFET后,单鳍即便再高,其驱动电流却很难随之提升。通过垂直堆叠纳米片状导电沟道,纳米片结构晶体管可以在标准单元内实现更大的有效沟道宽度。通过这种方式,纳米片结构的晶体管可以提供比鳍片更大的驱动电流,也是进一步微缩CMOS的基础。同时纳米片结构还允许可变的器件宽度,在设计中具备更高的灵活性。因为驱动电流有所增加,设计人员可以减少单元尺寸和电容,以降低每片之间的寄生电容。

▲标准单元微缩演进示意图

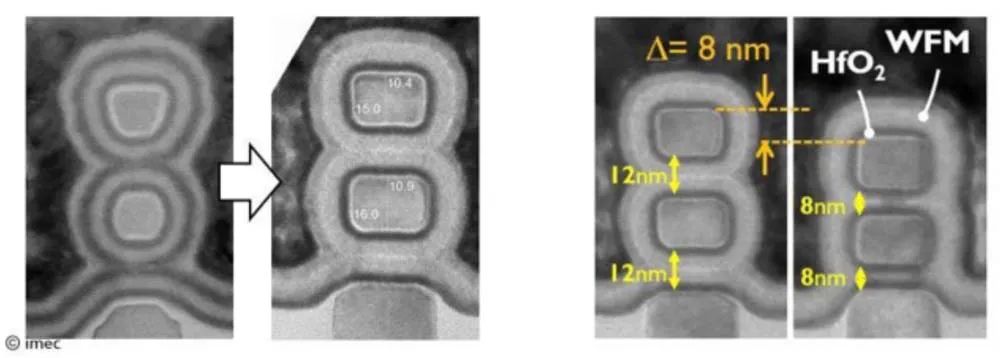

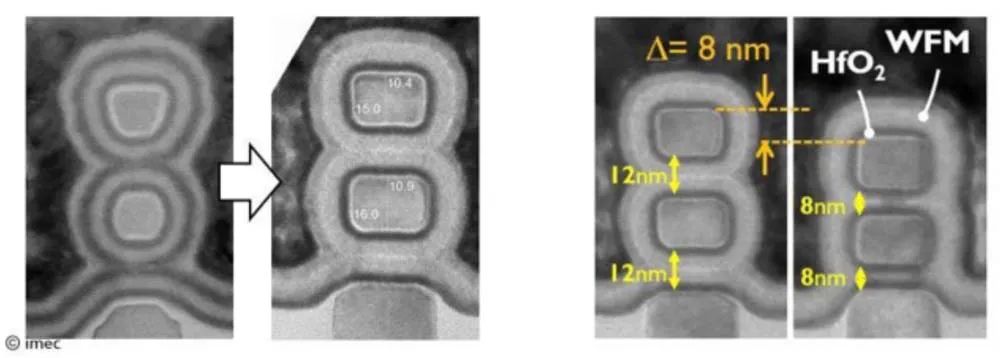

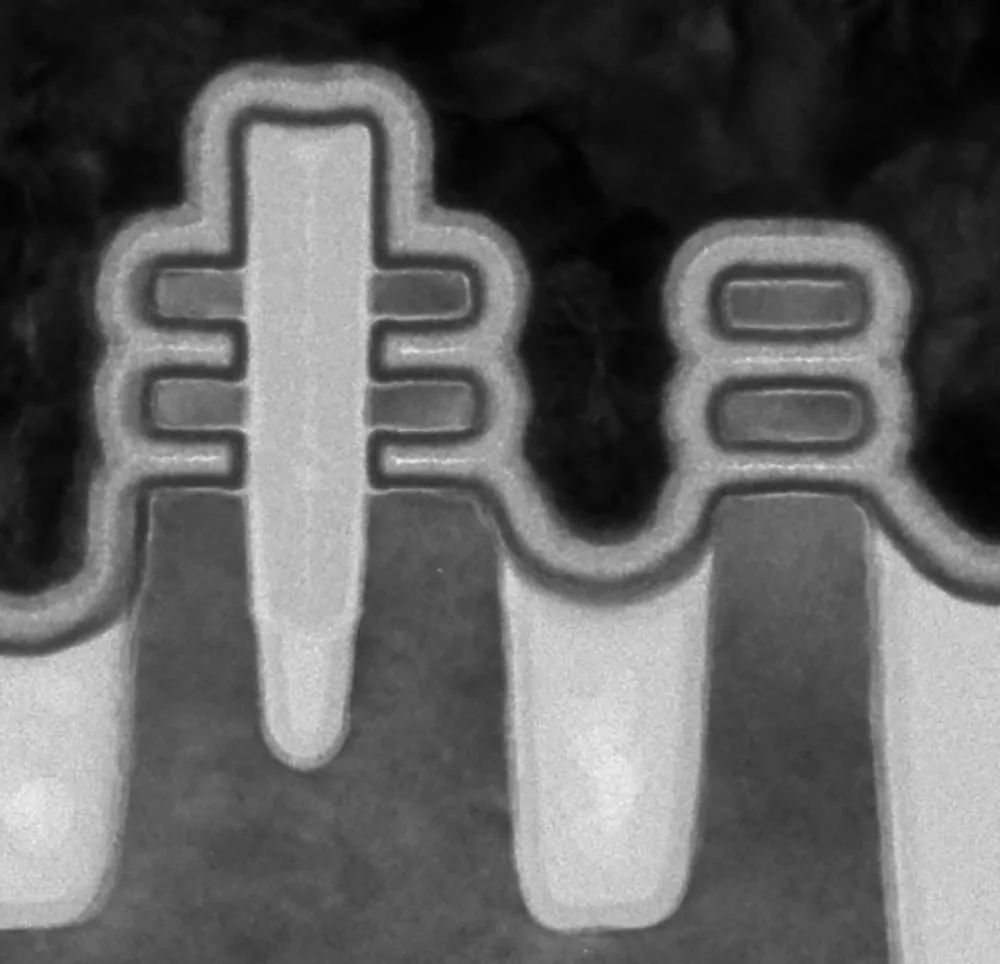

除了驱动电流和可变性,纳米片的环栅结构也优于FinFET结构。就像从平面MOSFET过渡到FinFET一样,全栅纳米片也伴随着新工艺集成挑战。幸运的是,纳米片基本算是FinFET的自然演变,许多为FinFET开发和优化的工艺模块可以重复使用。这无疑促进了纳米片结构在半导体行业中的应用,但也有很多工艺制程需要创新。IMEC确定了两个结构不同的4个关键工艺步骤,需要进行创新。第一,纳米片结构使用外延生长的多层Si和SiGe来作为器件沟道。器件沟道使用生长材料以及2种材料之间的晶格常数不同,是纳米片结构和传统CMOS器件的一大区别。在多层堆叠中,SiGe用作牺牲层(sacrifice),该层会在金属栅极替换工艺步骤中的沟道释放时移除。因为多层堆叠会以鳍的形式进行图案化,鳍片容易发生形变。在2017 IEDM会议上,IMEC提出了一个关键优化:实施浅沟槽隔离(STI)衬里,并在STI工艺步骤中使用低热来抑制氧化引起的鳍片变形。这不仅能够保持纳米片形状,也可以提高设备的直交流性能,即驱动电流和恒定功率下的速度增益。改进的交流性能可以转化为环形振荡电路的较低门延迟。第二,与FinFET不同的是,纳米片结构需要一个内部隔离物(inner spacer),即一种额外的电介质,将栅极与源极/漏极隔离以降低电容。内部隔离物的工艺中,横向蚀刻工艺会使多层堆叠结构中的SiGe层外部凹陷,产生小空腔,需要半导体厂商使用电介质材料填充这些空腔。这就是纳米片工艺流程中最复杂的工艺模块“内部间隔集成(Inner spacer integration)”,它需要高蚀刻选择性和精确的横向蚀刻控制,包括IMEC在内的全球多个研究团队解决了这一挑战。第三是纳米片沟道释放,即纳米片相互分离的步骤。正如前文所述,这种释放往往通过选择性的蚀刻掉多层SiGe来实现。该工艺中,需要半导体厂商进行高度选择性的蚀刻,简单来说就是尽量多地将纳米片间的Ge残留物蚀刻掉,同时不要使Si变得粗糙。这就需要研究人员控制静摩擦,以减少纳米片间的连接。IMEC对不同蚀刻工艺的研究为解决这一问题做出了较大贡献。第四个则是替代金属栅极(RMG)集成步骤,包括在纳米片层周围工作功能金属(work function metal)的沉积和图案化。2018年,IMEC强调了引述可扩展工作功能今数的重要性,从而减少了纳米片堆叠所占的垂直空间。IMEC曾展示了将两个垂直纳米片之间的间隔物从13nm减少到7nm,并将芯片的AC性能提升了10%。

▲垂直堆叠环栅纳米片晶体管的优化:改善纳米片形状控制(左),纳米片垂直空间缩减分离(右)

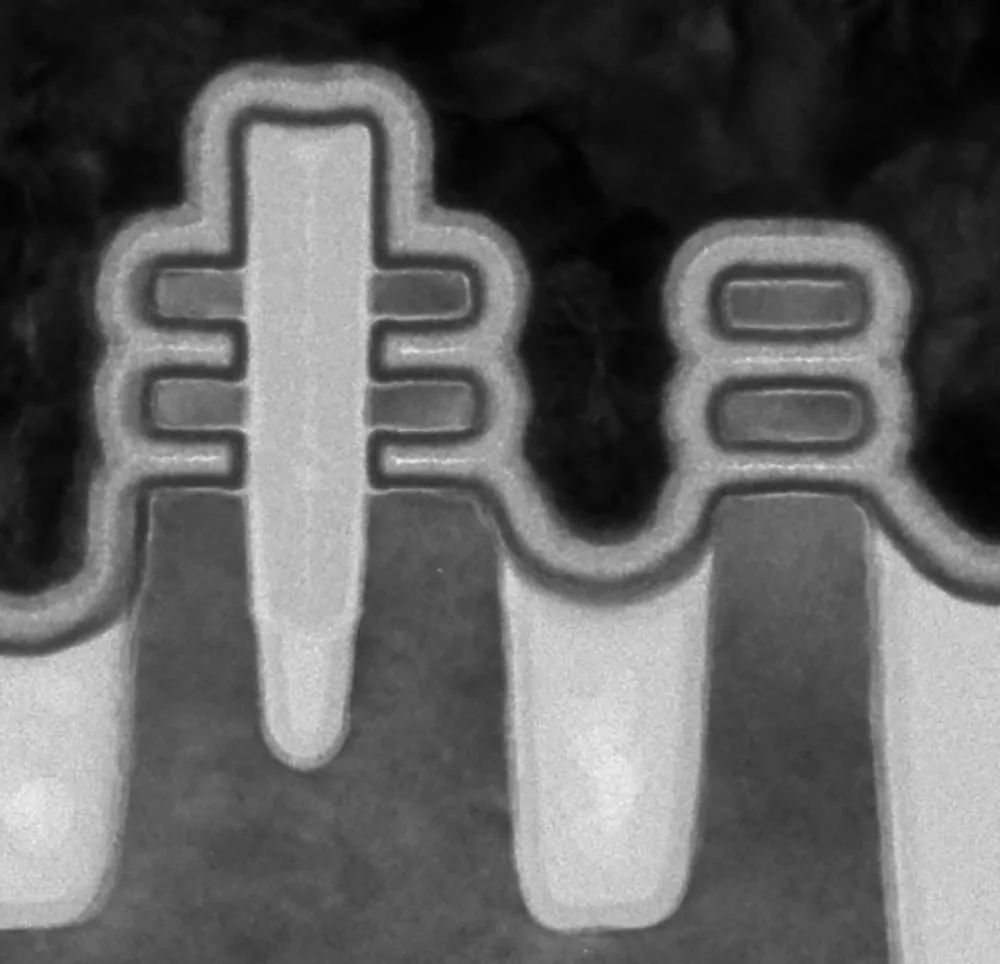

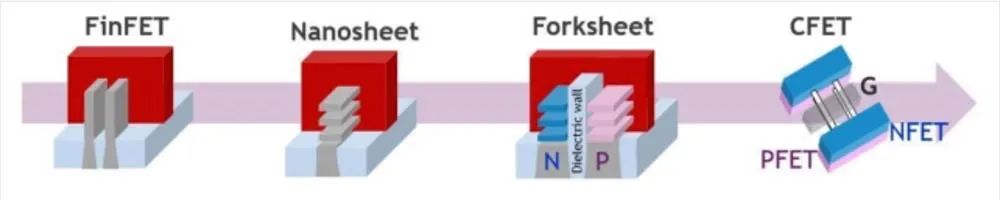

如果想要进一步提升直流性能,最有效的方法使扩大沟道的有效宽度。但是,在纳米片结构下,这变得非常困难。主要使因为n型和p型器件需要较大的空间,这使得在按比例微缩的单元高度上难以将纳米片的有效宽度扩大。2017年,IMEC首次公开提出Forksheet器件结构用来微缩SRAM,2019年IMEC又将这一器件结构用在逻辑芯片标准单元中。和纳米片结构相比,Forksheet在栅极图案化之前,通过在p和n型器件间引入介电墙,实现更小的n、p间距,进一步增强了沟道的有效宽度以及直流性能。这也让研究人员可以利用较小的n、p间隔,将标准单元的单元高度从5T推进到4T。仿真结果显示,Forksheet已比传统纳米片有10%的速度增益。这种性能提升的部分原因是由于栅极-漏极重叠较小而导致的(寄生)Miller电容减小。从工艺角度来看,Forksheet结构是从纳米片演变而来,2者的关键区别在于电介质壁的形成、改进的内部隔离层、源极/漏极外延和替换金属栅极步骤。在VLSI 2021会议上,IMEC首次展示了使用300mm Forksheet集成的Forksheet场效应器件的电气数据。双工作功能金属栅极可以在n-和pFET之间以17nm的间距集成,突出了Forksheet结构的关键优势。但是,Forksheet仍不完美。纳米片结构的环栅在很大程度上改善了对沟道的静电控制。Forksheet则采用了分叉形式的三门结构,似乎在静电控制上有所退步。

▲集成在一起的纳米片和Forksheet结构对比

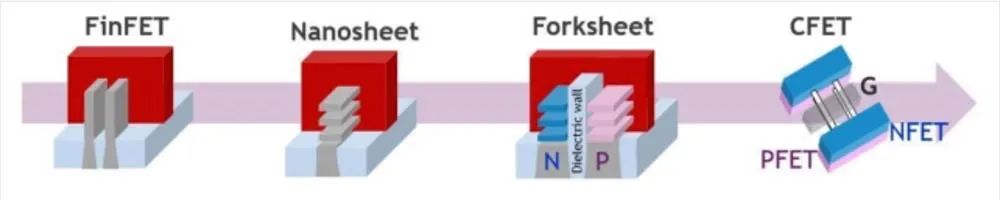

为了解决Forksheet的静电控制问题,CFET随即诞生。CFET结构可以进一步最大化有效沟道宽度,其中n极和p极堆叠在彼此顶部,可以进一步减小单元面积,扩大沟道宽度,推动标准单元到4T及以下。仿真证明,CFET对于逻辑芯片与SRAM尺寸微缩都有帮助。通过CFET,沟道可以制成鳍(n-fin on p-fin)或纳米片(n-sheet on p-sheet)的形式。而纳米片形式的CFET完善了纳米片结构的问题,是CMOS器件的最终结构。IMEC则在开发模块和集成工艺上有着很大的贡献,还量化了每个流程的功耗性能收益和复杂性。

▲从FinFET到CFET的晶体管结构演进过程

从处理角度来说,由于nMOS-pMOS垂直堆叠,CFET的结构较为复杂,有两种可能的集成方案,分别是单片集成(monolithic)和顺序集成(sequential),这两种集成方案则各有利弊。具体来说,单片CFET的成本较低,但是垂直集成十分复杂。单片CFET从底部沟道外延生长开始,然后是中间牺牲层的沉积,最后是顶部沟道的外延生长。当以纳米片沟道为目标时,起始的底部和顶部沟道配置可以是Si鳍片或Si/SiGe多层堆栈的形式。无论那种形式,堆叠都会导致非常高的垂直结构,这给鳍片、栅极、间隔和源/漏接触的进一步图案化带来了关键的挑战。例如,替换金属栅极集成步骤由于需要用于n和p不同的工作功能金属而更加复杂。在VLSI 2020上,IMEC率先展示了通过优化关键模块步骤实现的单片集成CFET结构。而相对来说,顺序CFET的集成流程较为简单。CFET顺序集成由几个模块组成,首先对底层器件进行处理。然后使用介电到介电晶片键合技术,通过晶圆转移在该层的顶部创建覆盖半导体层。最后,集成顶层器件,连接顶栅和底栅。因为底层和顶层设备都可以用传统的二维方式单独处理,所以顺序CFET可以灵活地集成用于n型和p型的不同沟道材料,进一步提升性能优势。但是作为新的方案,顺序CFET也需要解决一些挑战。第一个是涉及2个晶片之间键合介电氧化物厚度。过厚的氧化物会降低交流性能,但过薄的氧化物会产生键和缺陷风险。IMEC的薄键合氧化物工艺是解决氧化物厚度的一个方案,该工艺无键合空洞并且研发已经取得了进展。顺序CFET需要面对的第二个挑战是晶圆转移方法有热预算限制,需要降低顶层工艺温度到500°C避免对底层器件产生负面影响,而该工艺此前需要900℃。IMEC最近针对这两个问题提出了解决方案,可以在较低的处理温度下使栅极堆叠保持可靠性。一种是通过低温氢等离子体处理钝化硅氧化物夹层中的缺陷;第二种则是将界面偶极子Si引入沟道和HfO2栅极电解质之间,以抵消HfO2缺陷态和电荷载流子导带之间的能量。

回顾从FinFET到CFET的研发过程,每一代结构的改进都伴随着交流/直流性能的改进和标准单元高度的进一步降低。从处理的角度来看,纳米片结构可以被认为是FinFET结构的进化步骤。然而,每种不同的纳米片结构都面临着特定的集成挑战。随着芯片制程的不断发展,有能力继续追求先进制程的玩家越来越少。IMEC作为芯片制程工艺的重要研发力量,有力地推动了芯片制程的微缩。此前,IMEC CEO曾接受采访称,要将芯片制程推进1nm以内。无论如何,人们对于更高性能、更少功耗的追求不会改变。届时,先进制程的竞争可能会更加激烈。